DART Reconfigurable Architecture

To traditional performance and low-cost requirements, are nowadays added low-power consumption and flexibility constraints which imply the definition of new architectural paradigms. Coarse-grained dynamically reconfigurable architectures have recently emerged as efficient programmable structures in complex SoCs.

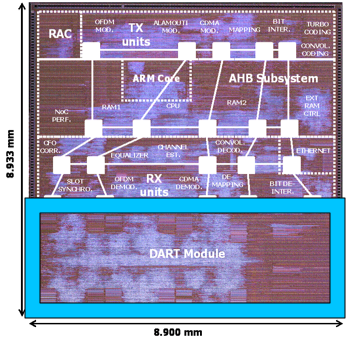

Our activity in this area of functional-level reconfigurable architecture has led to the definition of the DART architecture for mobile telecommunication applications. DART is a hierarchical architecture supporting different levels of parallelism. It is decomposed into clusters to exploit task parallelism. Each cluster of DART integrates two types of processing primitives: several Reconfigurable Data-Path (RDP) used for arithmetic processing and an FPGA core to process data at the bit level. We have studied reconfiguration schemes allowing high-performance, flexibility and low energy constraints to be supported. A computation power of 6.2 GOPS combined with an energy efficiency of 40 MOPS/mW demonstrate its potential in the context of multimedia mobile computing applications. This work has been conducted under a collaboration with STMicroelectronics (PHRASE project) and received funding from the French ministry of industry.

A silicon prototype of a DART cluster has then been realized in the framework of a collaboration with the LIST laboratory at CEA. The DART cluster implements the channel estimation in the 802.11a Wireless LAN norm. The synthesis of a DART cluster including six reconfigurable data-path and two dedicated dividers on a 130 nm CMOS technology from STMicroelectronics, leads to a 200 MHz clock frequency and 4.8 (32-bit) GOPS plus 400 MDivisionsPS) for less than 10 square millimeters.

A silicon prototype of a DART cluster has then been realized in the framework of a collaboration with the LIST laboratory at CEA. The DART cluster implements the channel estimation in the 802.11a Wireless LAN norm. The synthesis of a DART cluster including six reconfigurable data-path and two dedicated dividers on a 130 nm CMOS technology from STMicroelectronics, leads to a 200 MHz clock frequency and 4.8 (32-bit) GOPS plus 400 MDivisionsPS) for less than 10 square millimeters.

An efficient development flow is the key to exploit the computation power of functional- level reconfigurable architectures such as DART. Hence, a compilation framework has been defined [4]. It is based on the joint use of a front-end allowing the transformation and the optimization of the specification, a retargetable compiler (CALIFE) and an architectural synthesis tool. The development flow allows the user to describe its applications in the C language. After some automatic transformations (loop unrolling, loop kernel extractions, etc.), the distinction between regular codes, irregular ones and data manipulations permits to translate the high level description of the application into binary executable codes for DART. A cycle-accurate bit-accurate simulator developed in SystemC finally allows to validate the implementation and to evaluate its performance and energy consumption.

- S. Pillement, O. Sentieys, and R. David. DART: A Functional-Level Reconfigurable Architecture for High Energy Efficiency. EURASIP Journal on Embedded Systems (JES), pages 1-13, 2008. Article ID 562326, 13 pages. [ pdf ]

- R. David, S. Pillement, O. Sentieys, Energy-Efficient Reconfigurable Processsors, in “Low Power Electronics Design”, C. Piguet (editor), Computer Engineering, Vol 1, CRC Press, August 2004.

- R. David, D. Chillet, S. Pillement, and O. Sentieys. DART: A Dynamically Reconfigurable Architecture dealing with Next Generation Telecommunications Constraints. In Proceedings of the IEEE Int. Parallel and Distributed Processing Symposium, IPDPS'02, pages 156 - 163. IEEE CS Press, April 2002. [ pdf ]

- R. David, D. Chillet, S. Pillement, and O. Sentieys. A Dynamically Reconfigurable Architecture for Low-Power Multimedia Terminals. In SOC Design Methodologies, pages 51-62. Kluwer Academic Publishers, 2002. [ pdf ]

- R. David, D. Chillet, S. Pillement, and O. Sentieys. A Compilation Framework for a Dynamically Reconfigurable Architecture. In 12th IEEE International Conference on Field Programmable Logic and Applications, FPL 2002, volume 2438 of Lecture Notes in Computer Science (LNCS). Springer-Verlag, September 2002. [ pdf ]

- R. David, D. Chillet, S. Pillement, and O. Sentieys. Mapping future generation mobile telecommunication applications on a dynamically reconfigurable architecture. In IEEE International Conference on Acoustic Speech, and Signal Processing ICASSP 2002, pages IV-4194-IV-4197, May 2002. [ pdf ]

- R. David, D. Chillet, S. Pillement, O. Sentieys, A Dynamically Reconfigurable Architecture for Low-Power Multimedia Terminals, in 11th IFIP Int. Conference on VLSI and System On Chip, December 2001.

- J. Cambonie, S. Guérin, R. Keryell, L. Lagadec, B. Pottier, O. Sentieys, B. Weber, and S. Yazdani. Compiler and system techniques for SoC distributed reconfigurable accelerators. In A. Pimentel and S. Vassiliadis, editors, Proceedings of the Fourth International Workshop on Systems, Architectures, MOdeling, and Simulation SAMOS IV, volume 3133 of Lecture Notes in Computer Science (LNCS), Samos, Greece, July 2004. Springer-Verlag. [ pdf ]

- F. Ben Abdallah, S. Pillement, O. Sentieys, and A. Bouallegue. Acceleration of a vliw processor with dynamic reconfiguration. In The 16th International Conference on Microelectronics, pages 633-636, December 2004.