Teaching activity

- Responsible for the ''Embedded Systems'' branch of the SISEA (Signal, Images, Embedded Systems and Control) Master by Research (M2R) of Univ. Rennes (until 2020).

- Teaches mainly in the Electronics and Computer Engineering (SNUM) department of ENSSAT (Ecole Nationale Supérieure des Sciences Appliquées et de Technologie), a graduate engineering school of the University of Rennes 1 and in the Master SISEA.

- PSL-ITI (Paris Sciences & Lettres (PSL) Research University - Institute for Technology and Innovation), Innovative Technologies for Health program

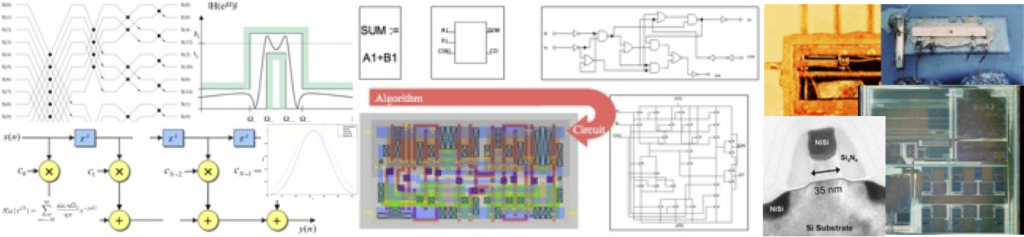

This year (2023), I teach two courses at ENSSAT: VLSI Integrated Circuits Design Methodologies, and VHDL - a Hardware Description Language for Simulation and Logic Synthesis.

Keywords: VLSI Design, RTL and Logic Synthesis, High-Level Synthesis, System-on-Chip, Optimization of Embedded Software, Low-Power Digital Systems, Discrete Signal & Systems, Digital Signal Processing, Wireless Sensor NetworksCourses in Embedded Systems and SoC Design

- Introduction to System-on-Chip

- ENSSAT/SNUM3, MASTER SISEA/SE slides part I slides part II

- High-Level Synthesis and Optimisation of HW and SW

- ENSSAT/SNUM3, MASTER SISEA/SE

- 1. Algorithmic transformations slides

- 2. High-Level Synthesis slides quelques corrections

- 3. High-Level Synthesis using CatapultC slides

- 3. Software Optimisation slides

- Travaux Dirigés, corrections TD, DS (2000-2010)

- VLSI Integrated Circuits Design Methodologies (slides 2019)

- ENSSAT/SNUM2

- 1. Introduction

- 2. CMOS Integrated Circuit Technologies

- 3. Design of CMOS Cells

- 4. IC Design Methods

- 5. Synchronous Design of IC

- VHDL: a Hardware Description Language for Simulation and Logic Synthesis (slides, appendix)

- ENSSAT/SNUM2

- 1. Introduction: Why HDLs?

- 2. Design Flow and Tools

- 3. Basic Language Concepts

- 4. Signal and Delay Models

- 5. Modeling Digital Systems

- 6. Concurrent and Sequential Processes

- Process statement, process event behavior, signals vs. variables, timing behavior of processes

- 7. Modeling Structures

- Structural models, generics, the Generate statement

- 8. Simulation and Validation

- Concepts, writing testbenches, configurations

- 9. RTL and Logic Synthesis

- Writing style for logic synthesis, combinational logic, sequential logic, RTL and logic synthesis CAD algorithms

- 10. Fil Rouge Example: FIR filter

- Gestion intelligente de l’énergie: aspects matériels et logiciels

- Telecom Bretagne, slides

Wireless Body Sensor Networks for Healthcare Applications: Challenges in Energy Consumption

Courses in Digital Signal Processing

- Digital Signal Processing/ Traitement numérique du signal

- ENSSAT/SNUM2 (1993-2005, 2013-2017), Plan et organisation du cours

- Polycopié du cours, Support du cours

- Travaux Dirigés

- TP sur Matlab (8h), Fichiers d'aide au TP

- Le filtrage numérique pour les nuls...

- JAVA Digital Filter Synthesis/ synthèse de filtres numériques JAVA

- Discrete Signals & Systems/ signaux et systèmes discrets

- ENSSAT/EII1 (2002-2006)

- Polycopié du cours, Support du cours (4pp)

Other Material (older)

- Projet de Conception d'ASIC (ENSSAT EII2)

- Conception et réalisation d'une chaîne de communication numérique CDMA

- Spécification détaillée, Présentation du projet, Simulation Matlab de référence

- Tutoriaux des outils de CAO utilisés

- Tutorial de l'outil MODELSIM

- Tutorial de l'outil SYNOPSYS (Version pdf)

- fichiers d'aide du tutorial

- Additif au tutorial de Synospys pour l'utilisation de SystemC (version pdf)

- Fichier d'aide pour l'utilisation de SystemC

- Tutorial de l'outil CADENCE

- Tutorial de l'outil COMPASS V9 (pour les nostalgiques...)

- TP Systèmes sur Puces (SoC) (ENSSAT EII3 / MASTER SISEA/SE)

- Partie 1 : Profiling d'applications décrites en C/C++

- Partie 2 : Traduction et simulation de la DCT inverse en SystemC (pdf)

- Partie 3 : Synthèse d'architecture avec Behavioral Compiler de Synopsys (pdf)

- Partie 4 : Synthèse d'architecture avec BSS (pdf)

- Présentation du TP (transparents)

- Fichiers d'aide au TP : tp_soc.tar, MPEG.tar, DCT.tar

- TD et TP en Conception d'ASIC (ENSSAT EII2)